# 電源電圧の動的再構成に基づく低消費電力並列 VLSIプロセッサの構成

藤 岡 与 周\*• 苫米地 宣 裕\*\*

## Design of a Low Power Parallel VLSI Processor Based on Dynamic Reconfiguration of Power Supply Voltages

Yoshichika Fujioka and Nobuhiro Томавесні

#### Abstract

To reduce the delay time and power consumption which are required especially for mobile-type intelligent integrated applications, we propose a parallel VLSI processor architecture based on dynamic reconfiguration of various kinds of multiplyadders and their power supply voltages. By changing the power supply voltages so that each gate utilized ratio becomes 100%, the power consumption can be reduced in proportion to the cube of the power supply voltage.

Key words: 微小遅れ時間 (small delay time), 知能集積システム (intelligent integrated system), 動的再構成 (dynamic reconfiguration), 低消費電力(low power consumption), 並列 VLSI プロセッサ (parallel VLSI processor)

## 1. まえがき

外界との相互作用を必要とする知能ロボットシステム などでは, 外界から入力される情報に基づく膨大な計算 が必要となるとともに、特に自立移動ロボットなどでは システムの低消費電力化が重要となる。また,外界との 相互作用では、外界から入力される情報に基づきアク チュエータ制御出力を計算する一連の直列的処理につい て, スループット向上とともにそれぞれの演算遅れ時間 を減少する必要がある。すなわち, 演算遅れ時間が小さ くかつ低消費電力という高性能並列 VLSI プロセッサ の開発が重要である。このため、これまでに種々の専用 並列プロセッサが開発されており、この分野はロボット エレクトロニクスと呼ばれている。本稿では,外界から の情報量に応じてサンプリング周期を可変にするシステ ムや、あるいは各サンプリング周期毎に計算量が異なる システムにおいて, ゲート稼働効率を最大にしかつ消費 電力を最小とするため、電源電圧の動的再構成という概 念に基づく並列 VLSI プロセッサの構成法を提案して いる。

### 2. データ依存グラフの特徴

知能ロボットシステムでは,膨大な量の多入力積和演算が必要となる。このような多入力積和演算を演算遅れ時間が短いという意味での高速かつ低消費電力で実行す

平成16年1月7日受理

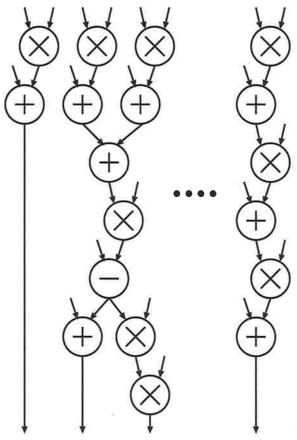

るためには、専用並列 VLSI プロセッサの開発が有用となる。専用並列 VLSI プロセッサを開発するためには、処理の流れとデータ依存関係をグラフで表現したデータ依存グラフ DFG の特徴を活用することが有用である。この場合、例えば図1に示すように DFG が規則的である場合には、ゲート稼働効率が高く演算遅れ時間の小さい専用並列 VLSI プロセッサの構成が比較的容易となる。

これに対し、図 2 に示すように DFG が必ずしも規則的でない場合には、最も演算遅れ時間が遅くなるパス(クリティカルパス)をできるだけ高速に処理するように専用並列 VLSI プロセッサが構成されるため、クリティカルパス以外のパス上の処理を担当する演算ユニットやゲート回路の稼働効率は必ずしも最大になるとは限らず、プロセッサ全体の総合的なゲート稼働効率は必ずしも高くならない。

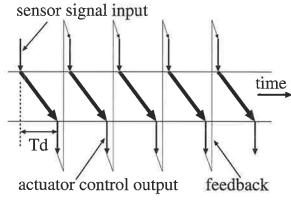

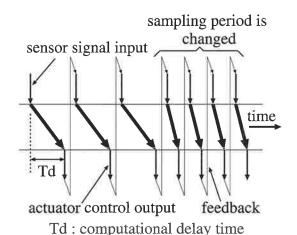

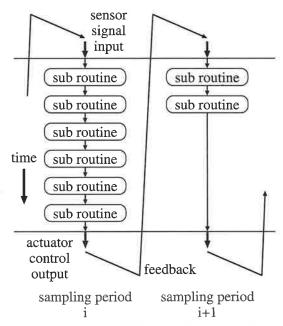

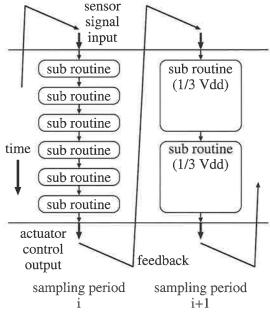

また、知能ロボットシステムなどでは、図3に示すように常に一定のサンプリング周期での処理が基本となるが、外界環境の変化に伴い、一時的に膨大な量の情報が入力されることが予想されるシステムでは、図4に示すようにサンプリング周期を可変にし、入力された情報量が特に多い場合や高精度作業が一時的に要求されるような場合に、サンプリング周波数を高くする必要があると考えられる。同様に、図5に示すように各サンプリング周期毎の計算量が変化することも考えられる。このようなシステムでは、最も計算量が多い場合に、要求される演算遅れ時間以内に処理を完了できる性能を備えた専用並列VLSIプロセッサが構成される。この場合、常に最大能力での計算が必要となるわけではないため、やはり

<sup>\*</sup> 八戸工業大学システム情報工学科助教授

<sup>\*\*</sup> 八戸工業大学システム情報工学科教授

図1 規則的なデータ依存グラフの例

専用並列 VLSI プロセッサの総合的な稼働効率は必ず しも高いとはいえないという問題がある。

さらに、知能ロボットシステムでは最初の設計段階で想定された処理内容が、ロボットの行動に伴い蓄積される種々の知見により改良され続ける可能性がある。このように、処理内容が変化し続ける状況において常にゲート稼働効率を高くかつ消費電力を低く保つことができる、専用の中の汎用性を備えた並列 VLSI プロセッサの開発が望まれている。

#### 3. 電源電圧の動的再構成

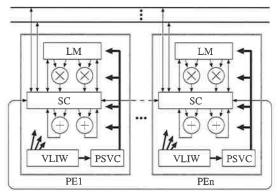

演算遅れ時間と消費電力をともに減少する新しい概念として、電源電圧の動的再構成を可能とする、図6に示す並列 VLSI プロセッサアーキテクチャを提案する。要素プロセッサ (PE) 内部に備えられた電源電圧コントローラ (PSVC) は、プログラムで指定される電源電圧を演算器などの各部に供給する機能を有している。このため、乗算器や加算器毎に別々の電源電圧を設定したり、あるいはすべての演算器に同じ電源電圧を設定することが可能である。

また、本並列 VLSI プロセッサは、知能ロボット制御

図2 不規則なデータ依存グラフの例

Td: computational delay time

図3 一定サンプリング周期の例

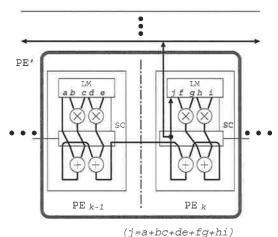

に必要となる種々の入力数の多入力積和演算器を動的に 再構成する機能も備えている。このため,通常のマイクロプロセッサのようにバス接続ではなく,演算器やメモリなどの間の直接接続を各プログラムステップ毎に動的に切換えるためのスイッチ回路(SC)とその内部の各スイッチを制御するためのVLIW(Very Long Instruction Word)制御回路が備えられている。高並列処理を可能とする多入力積和演算器の再構成の一例を図7に示す。バス接続などでは演算器間の中間データの転送が逐次的になりやすく,複数の演算器を並列に用いて演算遅

図4 可変サンプリング周期の例

図5 サンプリング周期毎に計算量が変化する例

れ時間を短くするような処理は困難であるのに対して、 提案する並列 VLSI プロセッサは演算器間の所望とす る直接接続が実現されるため高並列低遅延処理が可能で あるという特徴を有している。

このように、提案する動的再構成型並列 VLSI プロセッサは、高並列処理が可能であるとともに演算器など各部の電源電圧を動的に変化させることが可能となっている。これらの機能は、次の原理に基づく消費電力の減少のために備えられている。

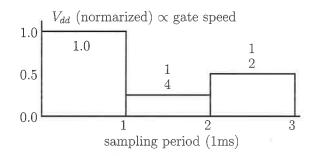

- ・ゲート速度は電源電圧 Vad に比例する。

- ・ゲート消費電力は  $V_{aa}^2$  とゲート動作回数(ゲート充放電回数)の積に比例する。

これらの原理に基づき,演算器など各部の電源電圧を, その時点で要求される処理速度となるように変化させる ことにより、常にゲート稼働効率をほぼ100%にするこ

⊗ : Multiplier LM: Local Memory VLIW: VLIW control

⊕ : Adder SC: Switch Circuit PE: Prosessor Element

PSVC: Power Supply Voltage (Vdd) Controller for each module

図6 電源電圧を動的に再構成可能な並列 VLSI プロセッサ

図7 多入力積和演算器の動的再構成

とができる。

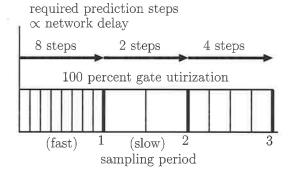

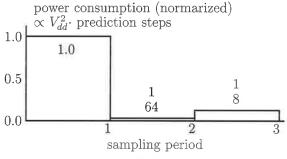

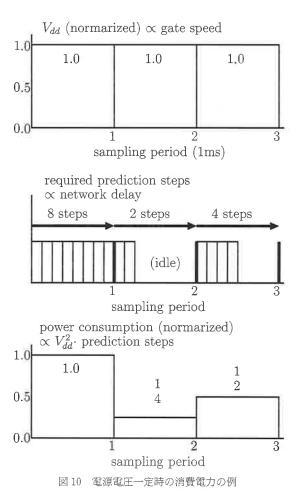

例えば,図5 に示すように各サンプリング周期毎に処理量が変化する場合には,図8 に示すように電源電圧を変化させ,常に100% のゲート稼働効率となるようにすることができる。上記2 つの基本原理によれば,ゲート速度は一定サンプリング周期毎のゲート動作回数に比例するため,結果としてゲート稼働効率100%動作状態での消費電力を $V_{ad}^{3}$  に比例して減少させることが可能となる。

さらに、ある処理を1台の PE で処理する場合とn台の PE で処理する場合とでは、ともにゲート稼働効率 が100%となるように電源電圧を変化させることにより、n台での並列処理により消費電力を $1/n^2$  に減少可能となる。この性質は、高並列処理が可能な動的再構成型並列 VLSI プロセッサの特長に適合するため、高並列処理と電源電圧の動的変更によるゲート稼働効率が高く消費電力の低い専用並列 VLSI プロセッサとして有用である。

サンプリング周期が一定である場合の, 各サンプリン

図8 ゲート稼働効率100%処理の例

図9 電源電圧の動的再構成における消費電力の例

グ周期毎の電源電圧,処理ステップ数,消費電力の一例 を図9と図10に示す。3つの各サンプリング周期毎に、8 ステップ,2ステップ,4ステップの単位処理が必要とな る場合を示している。図9ではゲート稼働効率が100% となるように電源電圧  $V_{dd}$  を変化させているため、各サ ンプリング周期毎の消費電力は Via に比例して減少し ている。これに対し、電源電圧が一定である場合には、ど の単位処理も最高速度で実行され, あとはアイドル状態 となり何も実行されない。この結果、ゲート稼働効率が 処理ステップ数に比例して変化することになる。同様に, 各サンプリングステップ毎の消費電力は処理ステップ数 に比例することになる。以上より、電源電圧を動的に変 化させてゲート稼働効率100%の状態で処理する場合 と,電源電圧が一定の場合のそれぞれの平均消費電力は, 図中の数値により求めるとそれぞれ 0.38 と 0.58 となる。 この結果、電源電圧の動的再構成に基づく並列 VLSI プ ロセッサを用いることにより、電源電圧が一定の場合の 処理と比較してゲート稼働効率 100% 状況下で 66% の 平均消費電力で処理を行なうことが可能である。

## 4. む す び

データ転送オーバヘッドが小さく高並列かつ演算遅れ時間の小さい処理が可能な動的再構成の概念に基づく並列 VLSI プロセッサアーキテクチャに, さらに電源電圧の動的再構成機能を備えることによる, ゲート稼働効率が高くかつ消費電力の小さい専用並列 VLSI プロセッサの構成法を明らかにした。本並列 VLSI プロセッサは, リングと多重バスで PE を接続するため拡張性が高く, 演算量と要求される演算遅れ時間にあわせて PE 数を容易に調整可能であるという特長も有しているため, 知能ロボットシステムなどにおける処理アルゴリズムの改善を容易に専用並列 VLSI プロセッサ上で実現可能であるという特長を有している。

本稿では、MOS FET の有する基本的性質に基づいて、電源電圧と消費電力の関係を1次近似して議論している。しかしながら、現実のデバイスでは本稿では考慮していない種々の要因により必ずしも本稿での議論が成り立たない場合もありうる。今後の課題として、電源電圧の動的再構成手法について回路レベルでの検討が必要となる。

さらに、本稿では電源電圧を変化させてゲート動作速度を調整し、ゲート稼働効率を常に最高とする手法を提案している。このような処理を実現するためには、通常の並列プロセッサにおけるスケジューリングやアロケーションアルゴリズムをそのまま適用するのではなく、必要に応じて各処理の処理時間を変化させてスケジューリングやアロケーションを効率的に行なうことが可能になると考えられる。この分野での新たな研究が期待される。

### 参考文献

- 1) 亀山, 藤岡: "ロボット用 VLSI プロセッサシステム", 日本ロボット学会誌, Vol. 14, No. 1, pp. 22-25 (1996).

- 2) 藤岡, 亀山: "ビットシリアルアーキテクチャに基づくロボット制御用再構成可能並列 VLSI プロセッサの構成", 電子情報通信学会論文誌 D-I, Vol. J81-D-I, No. 2, pp. 85-93 (1998).

- 3) Y. Fujioka, N. Tomabechi and M. Kameyama: "Design of a Parallel VLSI Processor for Tele-Robot Systems Based on Dynamic Reconfiguration of Power Supply Voltages," Proc. of SICE2003 Annual Conference, pp. 2638-2643, (2003).